Chip design is as a lot of an artwork as it’s an engineering feat. With all the doable layouts of logic and reminiscence blocks and the wires linking them, there are a seemingly infinite placement mixtures and infrequently, consider it or not, the most effective folks at chip floorplans are working from expertise and hunches and so they can’t at all times provide you with an excellent reply as to why a specific sample works and others don’t.

The stakes are excessive in chip design, and researchers have been making an attempt to take the human guesswork out of this chip format process and to drive towards extra optimum designs. The process doesn’t go away as we transfer in direction of chiplet designs, both, since all of these chiplets on a compute engine will must be interconnected to be a digital monolithic chip and all the latencies and energy consumption must be taken into impact for such circuit complexes.

This is a pure job, it could appear, for AI strategies to assist in chip design. It’s one thing that we talked about a few years in the past with Google engineers. The cloud large continues to pursue it: In March, scientists at Google Research launched PRIME, a deep-learning strategy that leverages present knowledge like blueprints and metrics round energy and latency to create accelerator designs which are sooner and smaller than chips designed utilizing conventional instruments.

“Perhaps the only doable approach to make use of a database of beforehand designed accelerators for {hardware} design is to make use of supervised machine studying to coach a prediction mannequin that may predict the efficiency goal for a given accelerator as enter,” they wrote in a report. “Then, one may doubtlessly design new accelerators by optimizing the efficiency output of this discovered mannequin with respect to the enter accelerator design.”

That got here a 12 months after Google used a way known as reinforcement studying (RL) to design layouts of its TPU AI accelerators. It’s not simply Google doing all this. Chip design device makers like Synopsys and Cadence are each implementing AI strategies into their portfolios.

Now comes Nvidia with an strategy that three of its deep studying scientists just lately wrote “makes use of AI to design smaller, sooner, and extra environment friendly circuits to ship extra efficiency with every chip technology. Vast arrays of arithmetic circuits have powered Nvidia GPUs to attain unprecedented acceleration for AI, high-performance computing, and laptop graphics. Thus, enhancing the design of those arithmetic circuits could be important in enhancing the efficiency and effectivity of GPUs.”

The firm made a run at RL with its personal take, calling it PrefixRL and saying the approach proved that AI can’t solely study to design circuits from scratch however that these circuits are smaller and sooner than circuits designed utilizing the most recent EDA instruments. Nvidia’s “Hopper” GPU structure, launched in March and increasing the corporate’s already expansive give attention to AI, machine studying and neural networks, accommodates virtually 13,000 situations of circuits designed utilizing AI strategies.

In a six-page analysis paper about PrefixRL, the researchers stated they targeted on a category of arithmetic circuits known as parallel-prefix circuits, which embody such circuits as adders, incrementors and encoders, all of which might be outlined at a better degree as prefix graphs. Nvidia wished to fined out whether or not an AI agent may design good prefix graphs, including that “the state-space of all prefix graphs is massive O(2^n^n) and can’t be explored utilizing brute power strategies.”

“A prefix graph is transformed right into a circuit with wires and logic gates utilizing a circuit generator,” they wrote. “These generated circuits are then additional optimized by a bodily synthesis device utilizing bodily synthesis optimizations similar to gate sizing, duplication, and buffer insertion.”

Arithmetic circuits are constructed utilizing logic gates like NAND, NOR and XOR and lots of wires, needs to be small so extra can match on a chip, quick to scale back any delay that may be a drag on efficiency and devour as little energy as doable. With PrefixRL, the researchers’ focus was on the scale of the circuit and the pace (for decreasing delay), which they stated are usually competing properties. The problem was discovering designs that almost all successfully used tradeoffs between the 2. “Put merely, we need the minimal space circuit at each delay,” they wrote.

“The ultimate circuit properties (delay, space, and energy) don’t straight translate from the unique prefix graph properties, similar to degree and node depend, as a consequence of these bodily synthesis optimizations,” the researchers wrote. “This is why the AI agent learns to design prefix graphs however optimizes for the properties of the ultimate circuit generated from the prefix graph. We pose arithmetic circuit design as a reinforcement studying (RL) process, the place we practice an agent to optimize the world and delay properties of arithmetic circuits. For prefix circuits, we design an atmosphere the place the RL agent can add or take away a node from the prefix graph.”

The design course of then legalizes the prefix graph to make sure it at all times maintains an accurate prefix sum computation and a circuit is then created from the legalized prefix graph. A bodily synthesis device then optimizes the circuit and the world and delay properties of the circuit are then measured. Throughout this course of, the RL agent builds the prefix graph by a collection of steps by including or eradicating nodes.

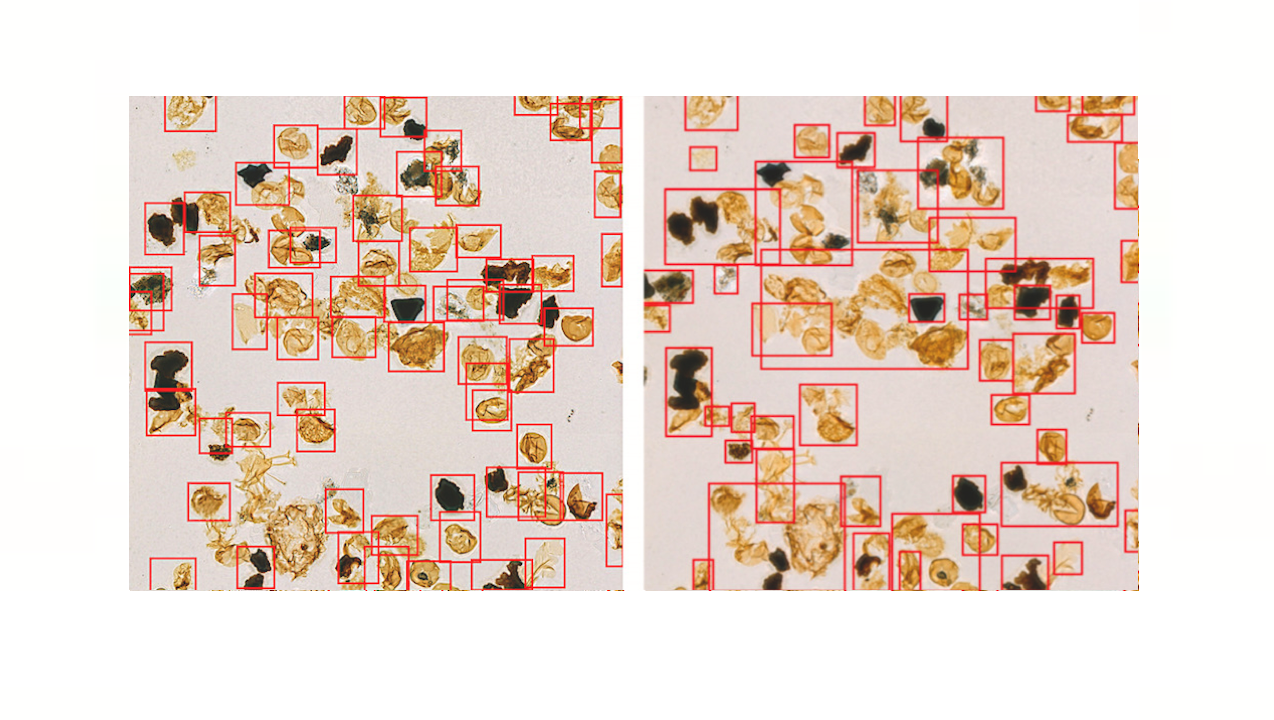

The Nvidia researchers used a totally convolutional neural community and the Q-learning algorithm – an RL algorithm – for his or her work. The algorithm educated the circuit design agent utilizing a grid illustration for prefix graphs, with every aspect within the grid mapping to a prefix node. The grid illustration was used at each the enter and output of the Q-network – with every aspect within the output grid representing Q-values for including or eradicating a node – and the neural community predicted the Q-values for the world and delay properties.

The compute calls for for operating PrefixRL have been important. The bodily simulation required 256 CPUs for every GPU and coaching too greater than 32,000 GPU hours, in line with the researchers. To handle the calls for, Nvidia created a distributed reinforcement studying platform dubbed “Raptor” that leveraged Nvidia {hardware} particularly for this degree of reinforcement studying.

“Raptor has a number of options that improve scalability and coaching pace similar to job scheduling, customized networking, and GPU-aware knowledge constructions,” they wrote. “In the context of PrefixRL, Raptor makes the distribution of labor throughout a mixture of CPUs, GPUs, and Spot situations doable. Networking on this reinforcement studying utility is numerous and advantages from … Raptor’s capability to change between NCCL [Nvidia Collective Communications Library] for point-to-point switch to switch mannequin parameters straight from the learner GPU to an inference GPU.”

The community additionally benefited from the Redis retailer used for asynchronous and smaller messages like rewards and statistics and a JIT-compiled RPC for high-volume and low-latency requests similar to importing expertise knowledge. Raptor additionally included GPU-aware knowledge constructions for such duties as batching knowledge in parallel and prefetching it onto the GPU.

The researchers stated that the RL brokers have been in a position to design circuits based mostly solely on studying with suggestions from synthesized circuit properties, with outcomes that use 64b adder circuits designed by PrefixRL. The greatest such adder delivered 25 % decrease space than the EDA device adder and the identical delay.

“To the most effective of our data, that is the primary methodology utilizing a deep reinforcement studying agent to design arithmetic circuits,” the researchers wrote. “We hope that this methodology could be a blueprint for making use of AI to real-world circuit design issues: developing motion areas, state representations, RL agent fashions, optimizing for a number of competing goals, and overcoming sluggish reward computation processes similar to bodily synthesis.”

https://www.nextplatform.com/2022/08/08/using-ai-chips-to-design-better-ai-chips/