Researchers from MIT and NVIDIA have formulated two methods that speed up the processing of sparse tensors (Tensors function elementary information constructions in machine studying fashions, appearing as multi-dimensional arrays that set up and retailer information).

The aim of each new methods is to take benefit of the tensors zero values successfully. It is feasible to deal with these tensors with out processing the zeros, which saves reminiscence and computation. For instance, multiplying something by zero leads to zero, subsequently, that operation could be skipped. Additionally, it will probably compress the tensor, permitting for extra to be saved in on-chip reminiscence as a result of zeros don’t should be stored.

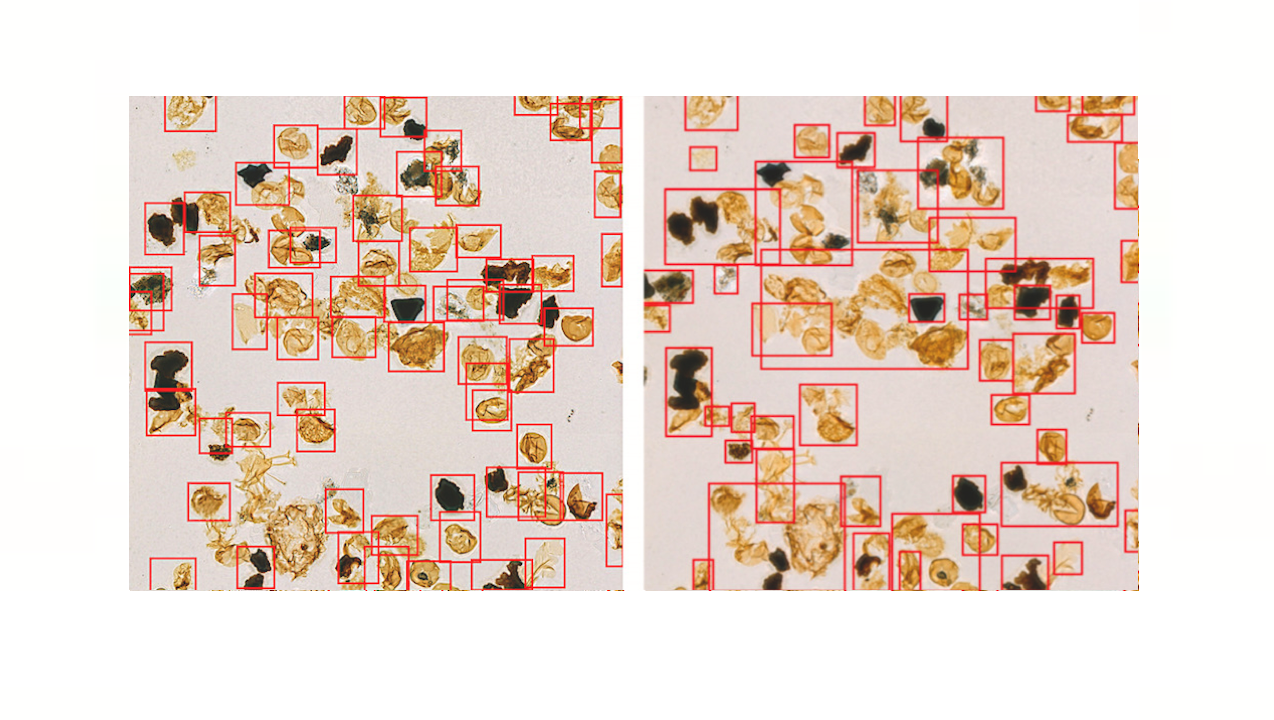

Sparsity in tensors happens when pointless parts are eliminated by changing some values with zeros, a course of often known as pruning. The diploma of sparsity and the positions of these zeros can differ throughout fashions. Researchers usually constrain the places of nonzero values to facilitate finding them in massive fashions. The adaptability of {hardware} accelerators is restricted as a result of they’re often designed for explicit sparsity patterns.

The analysis crew have developed a {hardware} accelerator referred to as HighLight, which is succesful of effectively dealing with numerous sparsity patterns. The researchers have used hierarchically structured sparsity to effectively signify differing kinds of sparsity patterns made up of easier ones. In this technique, they break down the numbers in a set into smaller teams, and every group follows a easy sample. These smaller teams are then mixed into bigger teams, forming a hierarchy. Each assortment of teams additionally follows a easy sample (like having one group with zeros and three teams with out in a degree with 4 teams). This course of continues with bigger ranges, however the patterns keep easy at every step.

This simplicity allows HighLight to seek out and skip zeros extra effectively, so it will probably take full benefit of the alternative to chop extra computation. Their accelerator design had about six instances higher energy-delay merchandise (a metric associated to vitality effectivity) than different approaches.

Researchers can even leverage sparsity to maneuver and course of information on a pc chip extra effectively. Since the tensors are sometimes bigger than what could be saved in the reminiscence buffer on the chip, the chip solely grabs and processes a bit of the tensor at a time. The chunks are referred to as tiles. To maximize the buffer’s capability and reduce how often the chip should entry exterior reminiscence.

To maximize the buffer’s capability and scale back the quantity of instances the chip must entry exterior reminiscence (which could be energy-intensive and decelerate processing), researchers goal to make use of the largest doable tile that matches into the buffer.

Since many information values are zero, a bigger tile can match into the buffer than its uncooked capability would possibly counsel, as zero values don’t should be saved. However, the quantity of zero values can range throughout totally different components of the information, and subsequently, it will probably additionally differ for every tile.

To take care of this, the analysis group prompt utilizing an overbooking method to permit for a rise in tile dimension. In a sparse information set, a tile dimension could be chosen so that most tiles have sufficient zeros to suit into the buffer. Occasionally, a tile might have extra non-zero values than the buffer can accommodate. In such circumstances, these extra information are pushed out of the buffer.

The analysis group has empowered the {hardware} to retrieve solely the displaced information with out fetching and processing the complete tile once more. They obtain this by modifying the “tail finish” of the buffer, resulting in the method’s identify, Tailors.

Additionally, they developed an method, named Swiftiles, to find out the tile dimension effectively, capitalizing on the advantages of overbooking. Swiftiles scale back the frequency with which the {hardware} should examine the tensor to establish an optimum tile dimension, thereby saving on computational sources.

The mixture of Tailors and Swiftiles leads to a efficiency increase, doubling the velocity whereas requiring solely half the vitality consumption in comparison with present {hardware} accelerators that can not deal with overbooking.

According to the researchers, Swiftiles can estimate the optimum tile dimension with out requiring a number of iterations to refine the estimate. This course of is feasible as a result of of the assist for overbooking. Even with a big estimation error, notable speedup could be achieved as a consequence of a particular distribution of non-zero values.

Check out the Paper 1, Paper 2, and MIT Research Blog. All credit score for this analysis goes to the researchers of this mission. Also, don’t neglect to hitch our 32k+ ML SubReddit, 41k+ Facebook Community, Discord Channel, and Email Newsletter, the place we share the newest AI analysis information, cool AI tasks, and extra.

If you want our work, you’ll love our e-newsletter..

We are additionally on Telegram and WhatsApp.

Rachit Ranjan is a consulting intern at MarktechPost . He is presently pursuing his B.Tech from Indian Institute of Technology(IIT) Patna . He is actively shaping his profession in the area of Artificial Intelligence and Data Science and is passionate and devoted for exploring these fields.

🔥 Meet Retouch4me: A Family of Artificial Intelligence-Powered Plug-Ins for Photography Retouching

https://www.marktechpost.com/2023/11/12/researchers-from-mit-and-nvidia-developed-two-complementary-techniques-that-could-dramatically-boost-the-speed-and-performance-of-demanding-machine-learning-tasks/